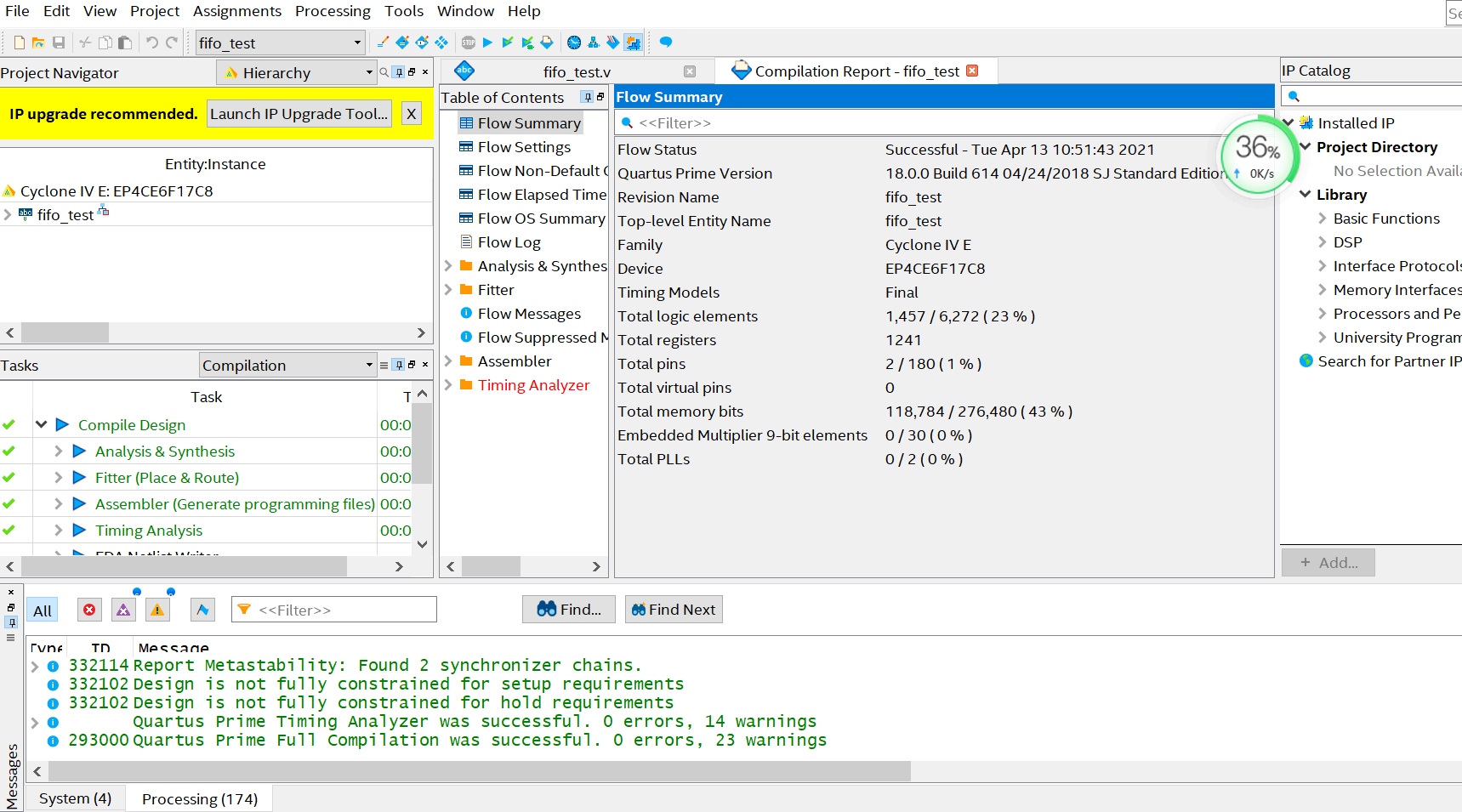

FPGA片内FIFO读写测试Verilog逻辑源码Quartus工程文件+文档说明,使用 FPGA 内部的 FIFO 以及程序对该 FIFO 的数据读写操作。FPGA型号Cyclone4E系列中的EP4CE6F17C8,Quartus版本17.1。

timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

module fifo_test(

input clk, //50MHz时钟

input rst_n //复位信号,低电平有效

);

//-----------------------------------------------------------

localparam W_IDLE = 1;

localparam W_FIFO = 2;

localparam R_IDLE = 1;

localparam R_FIFO = 2;

reg[2:0] write_state;

reg[2:0] next_write_state;

reg[2:0] read_state;

reg[2:0] next_read_state;

reg[15:0] w_data; //FIFO写数据

wire wr_en; //FIFO写使能

wire rd_en; //FIFO读使能

wire[15:0] r_data; //FIFO读数据

wire full; //FIFO满信号

wire empty; //FIFO空信号

wire[8:0] rd_data_count;

wire[8:0] wr_data_count;

///产生FIFO写入的数据

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

write_state <= W_IDLE;

else

write_state <= next_write_state;

end

always@(*)

begin

case(write_state)

W_IDLE:

if(empty == 1'b1) //FIFO空, 开始写FIFO

next_write_state <= W_FIFO;

else

next_write_state <= W_IDLE;

W_FIFO:

if(full == 1'b1) //FIFO满

next_write_state <= W_IDLE;

else

next_write_state <= W_FIFO;

default:

next_write_state <= W_IDLE;

endcase

end

assign wr_en = (next_write_state == W_FIFO) ? 1'b1 : 1'b0;

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

w_data <= 16'd0;

else

if (wr_en == 1'b1)

w_data <= w_data + 1'b1;

else

w_data <= 16'd0;

end

///产生FIFO读的数据

always@(posedge clk or negedge rst_n)

begin

if(rst_n == 1'b0)

read_state <= R_IDLE;

else

read_state <= next_read_state;

end

always@(*)

begin

case(read_state)

R_IDLE:

if(full == 1'b1) //FIFO满, 开始读FIFO

next_read_state <= R_FIFO;

else

next_read_state <= R_IDLE;

R_FIFO:

if(empty == 1'b1)

资源简介:FPGA片内FIFO读写测试Verilog逻辑源码Quartus工程文件+文档说明,使用 FPGA 内部的 FIFO 以及程序对该 FIFO 的数据读写操作。FPGA型号Cyclone4E系列中的EP4CE6F17C8,Quartus版本17.1。timescale 1ns / 1ps/////////////////////////////////////////////////...

上传时间: 2021-12-19

上传用户:20125101110

资源简介:lm75A温度数字转换器 FPGA读写实验Verilog逻辑源码Quartus工程文件+文档资料,FPGA为CYCLONE4系列中的EP4CE6E22C8. 完整的工程文件,可以做为你的学习设计参考。LM75A 是一个使用了内置带隙温度传感器和模数转换技术的温度数字转换器。它也是一个温度检测器,...

上传时间: 2021-10-27

上传用户:ooaaooxx

资源简介:基于FPGA设计的vga显示测试实验Verilog逻辑源码Quartus工程文件+文档说明,FPGA型号Cyclone4E系列中的EP4CE6F17C8,Quartus版本17.1。module top( input clk, input rst_n, //vga outpu...

上传时间: 2021-12-19

上传用户:kingwide

资源简介:基于FPGA设计的sdram读写测试实验Verilog逻辑源码Quartus工程文件+文档说明,DRAM选用海力士公司的 HY57V2562 型号,容量为的 256Mbit,采用了 54 引脚的TSOP 封装, 数据宽度都为 16 位, 工作电压为 3.3V,并丏采用同步接口方式所有的信号都是时钟信号。FPGA型号...

上传时间: 2021-12-18

上传用户:lostxc

资源简介:基于FPGA设计的字符VGA LCD显示实验Verilog逻辑源码Quartus工程文件+文档说明,通过字符转换工具将字符转换为 8 进制 mif 文件存放到单端口的 ROM IP 核中,再从ROM 中把转换后的数据读取出来显示到 VGA 上,FPGA型号Cyclone4E系列中的EP4CE6F17C8,Quartus...

上传时间: 2021-12-18

上传用户:jimmy950583

资源简介:FPGA读写SD卡读取BMP图片通过LCD显示例程实验 Verilog逻辑源码Quartus工程文件+文档说明,FPGA型号Cyclone4E系列中的EP4CE6F17C8,Quartus版本17.1。1 实验简介在前面的实验中我们练习了 SD 卡读写,VGA 视频显示等例程,本实验将 SD 卡里的 BMP 图片读出,写...

上传时间: 2021-10-27

上传用户:ibeikeleilei

资源简介:FPGA采样AD9238数据并通过VGA波形显示例程 Verilog逻辑源码Quartus工程文件+文档说明,FPGA型号Cyclone4E系列中的EP4CE6F17C8,Quartus版本17.1。ADC 模块型号为 AN9238,最大采样率 65Mhz,精度为12 位。实验中把 AN9238 的 2 路输入以波形方式在 HDMI 上显示...

上传时间: 2021-10-27

上传用户:qingfengchizhu

资源简介:FPGA读取OV5640摄像头数据并通过VGA或LCD屏显示输出的Verilog逻辑源码Quartus工程文件+文档说明,FPGA型号Cyclone4E系列中的EP4CE6F17C8,Quartus版本17.1。module top( input clk, input ...

上传时间: 2021-12-18

上传用户:yiyewumian

资源简介:atmega8的片内eeprom读写操作程序,已通过调试。

上传时间: 2013-12-17

上传用户:气温达上千万的

资源简介:实现c8051f310的片内flash读写

上传时间: 2016-12-15

上传用户:redmoons